TIMETECH

# Development and test of a low-cost ground terminal for ACES-MWL

W. SCHÄFER<sup>1</sup>, T. Schwall<sup>1</sup>, S. Liu<sup>1</sup>, T. Feldmann<sup>1</sup>

<sup>1</sup> **TimeTech GmbH**, Stuttgart, Germany wolfgang.schaefer@timetech.de

#### Outline

#### **Objective 1: Make at least 1 G/T operational**

- Revival of the old Computer Infrastructure

- Re-Evaluate Earlier Measurements

- Activities with the G/T RF EGSE

- Improved T&F Infrastructure

- Short- and long-term performance

#### **Objective 2: Modernise G/T hardware**

- 2-way: Current state-of-the-art, where to go?

- Cost Reduction...

- Digital Implementation, SATRE TWSTFT

- Breadboarding

#### Outlook

#### **Revival of the old Computer Infrastructure, VMware**

#### 🗋 EM-Server

- DataCollector-ACES-7.19 use for EM\_migrated

- DataRecorder-ACES-21-4 use for EM\_migrated

- Free\_MWL\_EM\_123.99 use for EM\_migrated

- SLES11.1-64-ACES-2 GT-42

- X2-VM-123.73 ACES GT-3 controller use for EM\_migra

- X2-VM-123.93 GT-2 Controller use for EM\_migrated

- X2-VM-73clone ACES GT Controller-2

- 📅 X3-VM-74-i3 ACES EM use for EM\_migrated

- X4-VM-75 MWL EGSE controller use for EM\_migrated

- X5-VM76-i3 EGSE Controller use for EM\_migrated

FM Blue Box Veeam-Server: 22-10-19 14:24:23

**EM Server:** 10 virtual machines running, incl G/T controller

- 📋 FM Blue Box

- FS-DataCollector-ACES-19\_restored

- 🔂 FS-FeeNAS-99\_restored

- FS-SLES12SP2-DR-MWL-21

- 🔂 SLES11.1-64-ACES-1 FS-43

- X3-FS-Analyser-74\_restored

- 🔂 X3-VM-74clone-FS

Development and test of a low-cost ground terminal

- X4-FS-Power control-75\_restored

- X4-VM-75clone-FS (do not use, use EM instead)

- X5-FS-RF-EGSE Control-Z6 allways off\_restored Veeam-Server: 22-10-19 14:25:46

**FM Blue Box** (part of EGSE) 8 virtual machines running

The full set of M&C computers has been restored from backup, is again available in virtualised environment (VMware)

3

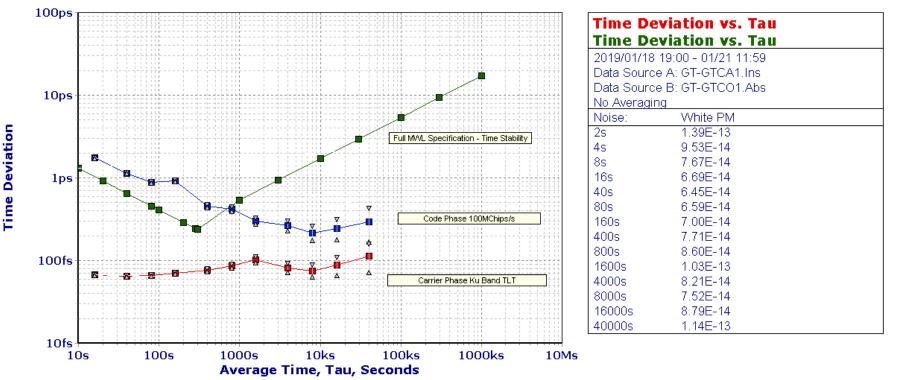

#### Re-Evaluate Earlier Measurements (read from database) top: Code Phase, bottom: Carrier Phase

DataAnalyzer v3.4 © TimeTech GmbH 2011

## G/T with continuous Test-Loop Translator, carrier phase stays at 100 fs for 3 days

Database and data-analysis fully functional

Development and test of a low-cost ground terminal

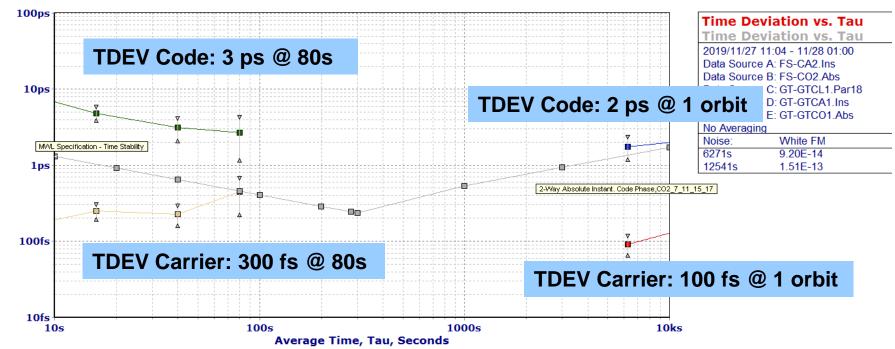

#### **Re-Evaluate Earlier Measurements (2), End-to-End Test**

DataAnalyzer v3.4 © TimeTech GmbH 2011

**Time Deviation**

- Lambda config, FS & G/T with realistic orbits, incl. Doppler

- Right data: 1 point / orbit

- Reproducible, estimate carrier cycle / orbit

- TDEV carrier phase: 100 fs in the long run

TIMET

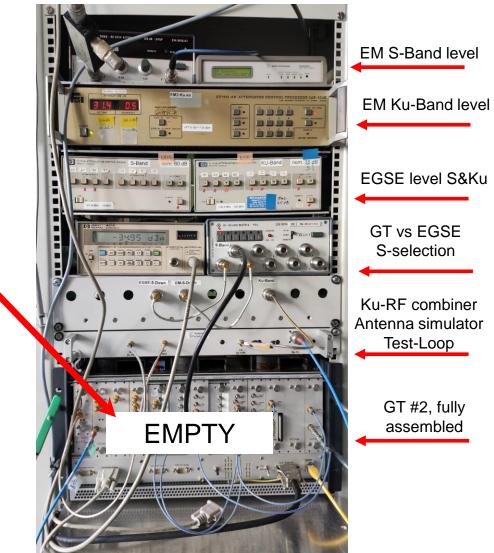

#### Activities with the G/T RF EGSE: ready to accept test items

**The right picture** is from my last presentation 2019, holding GT #2

Today, the G/T drawer (above) is mostly empty, awaiting modules to be tested.

Otherwise, the G/T RF EGSE is unchanged

IWG, Paris 2022-10-20, ws

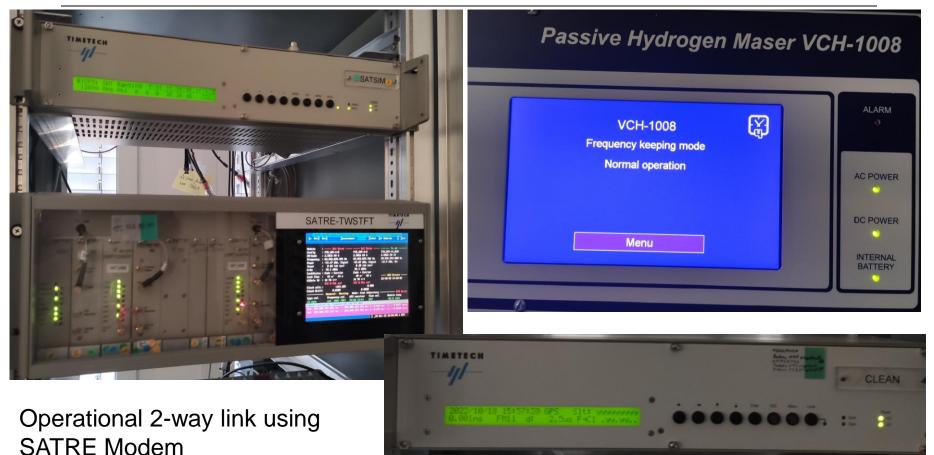

#### Improved T&F Infrastructure, Hardware

RAKON USO: 4E-14@ 1s, locked to PHM Steered to UTC(PTB) via 2-way, time constant 1 day

Development and test of a low-cost ground terminal

#### TIMETECH

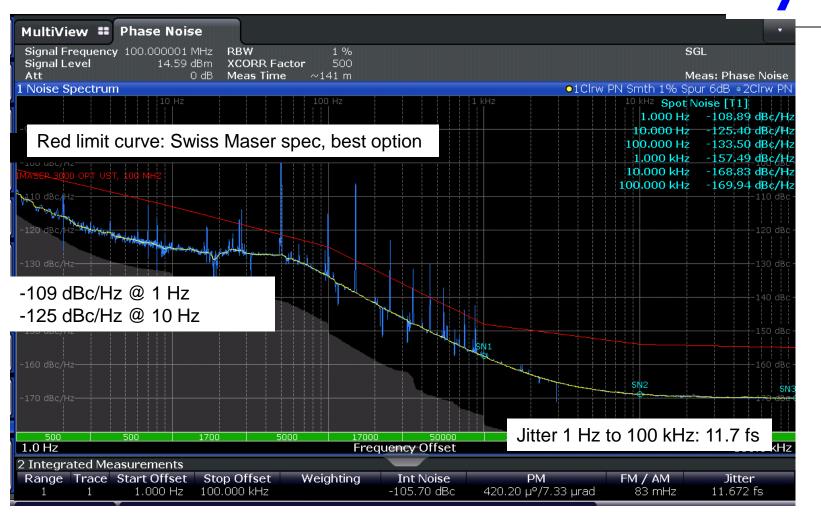

#### Improved T&F Infrastructure, 100 MHz Phase Noise

#### PN of 100 MHz signal approx 10 dB better than best Swiss Maser Test equipment: R&S FSWP

IWG, Paris 2022-10-20, ws

Development and test of a low-cost ground terminal

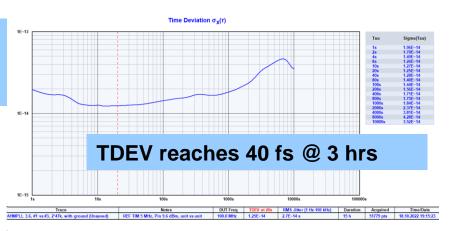

#### **Improved T&F Infrastructure, Phase Measurements**

Modified Allan Deviation (Mod  $\sigma_{v}(\tau)$ )

Comparison between two 100 MHz generators 15 hrs

Development and test of a low-cost ground terminal

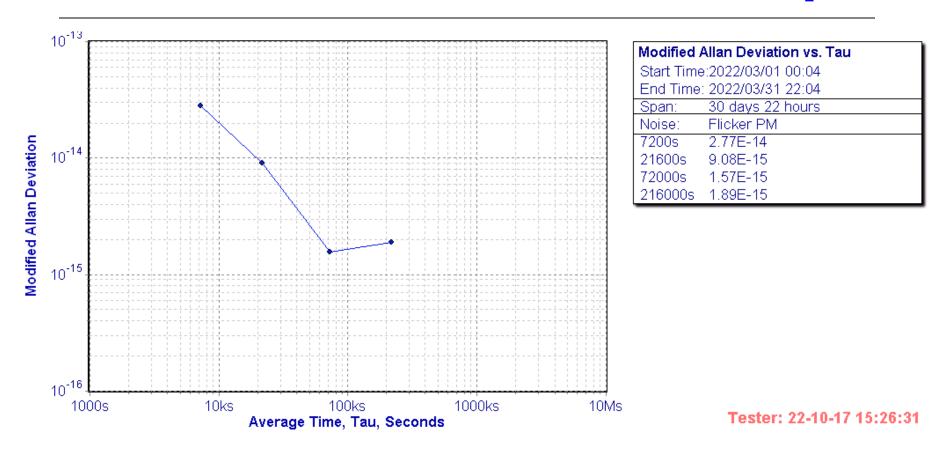

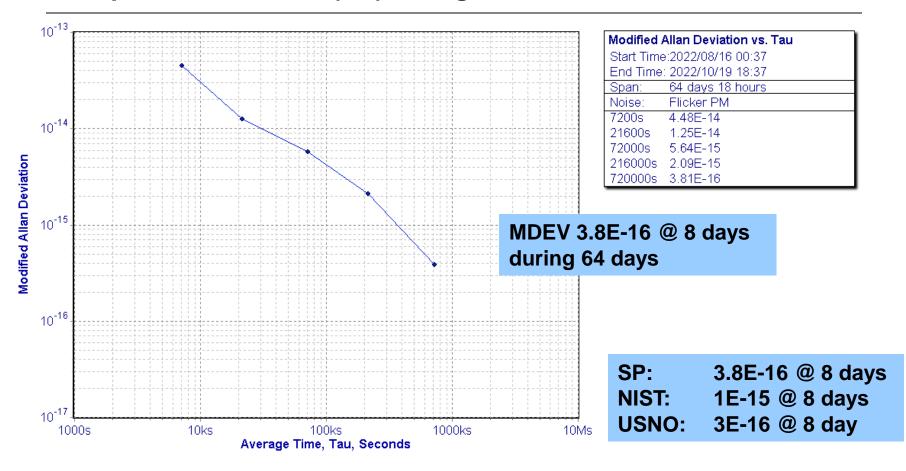

#### **T&F Infrastructure, PHM long-term performance**

#### Free-running PHM VCH-1008, compared to UTC(PTB), March 2022 Approx 1.5E-15 @ 1 day

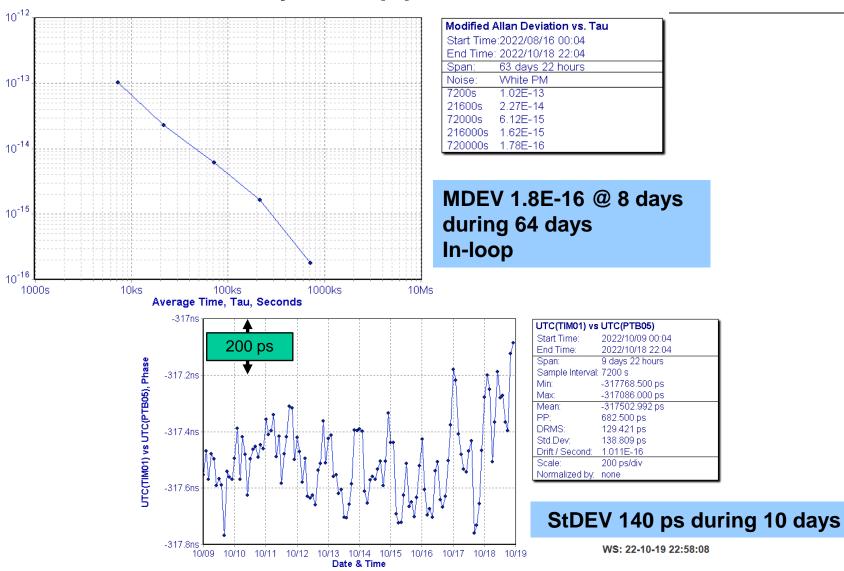

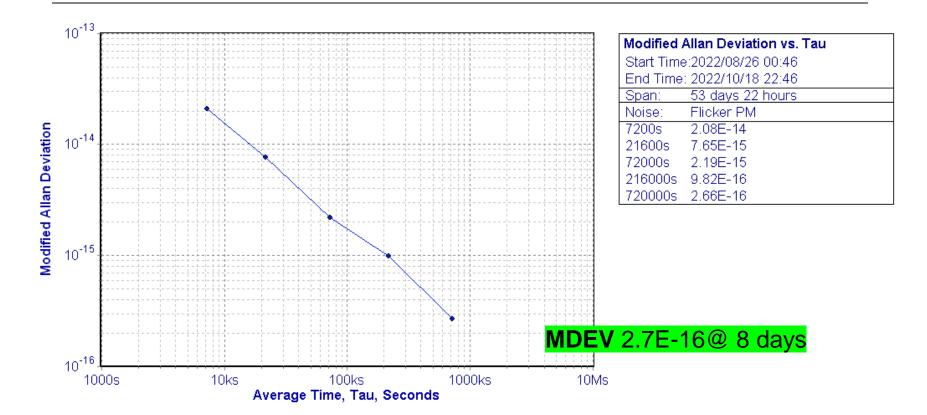

#### T&F Infrastructure, PHM locked to UTC(PTB), time constant 1 day, in-loop performance, ITU-files

IWG, Paris 2022-10-20, ws

### T&F Infrastructure, PHM locked to UTC(PTB), compared to Sweden (SP), using ITU-files

Proof: compare to other, independent time scales

IWG, Paris 2022-10-20, ws

#### 2-way: Current state-of-the-art: where to go?

From the BIPM web server: PTB vs USNO (best Ua 200 ps)

https://webtai.bipm.org/ftp/pub/tai/timelinks/lkc/2207/usnoptb/lnk/usnoptb.t3b3\_.gif

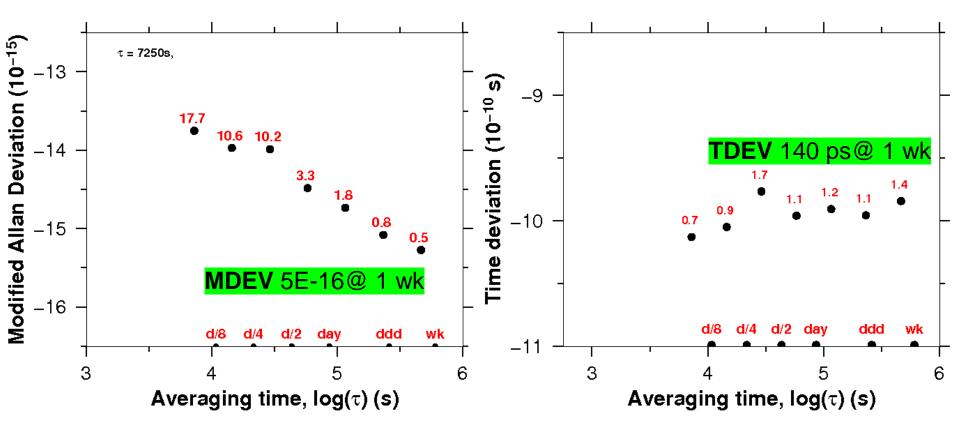

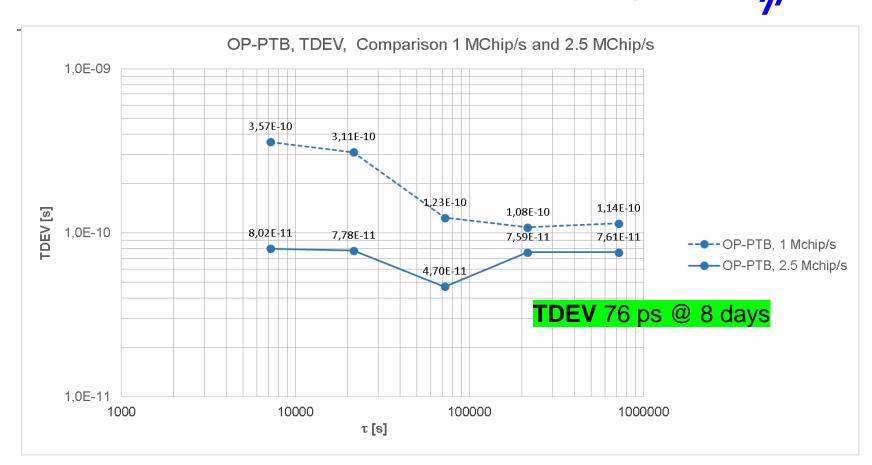

#### **OP - PTB**, 2021-2022, 1 MChip/s vs 2.5 MChip/s, 54 days

Expected improvement by increasing the chip rate, 1...2.5 MChip/s

Current systems fall short in the view of science and clock developments, like ACES: 1E-17 and far away from 1E-18 goals, which are around

IWG, Paris 2022-10-20, ws

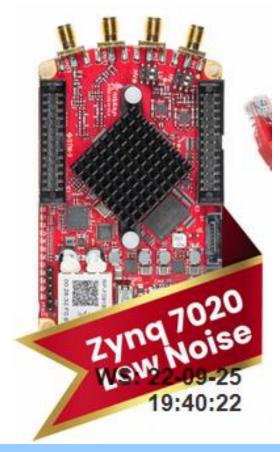

#### **Cost Reduction:** Digital Implementation

Zynq 7020: 125 MSa/s, SATRE: 20 MCh/s and higher

Digital implementation of SATRE Full set of features, ongoing

Red Pitaya 250MSa/s, 1 pps input

Compatible with MWL signal structure, code and carrier

**Activity started**

Development and test of a low-cost ground terminal

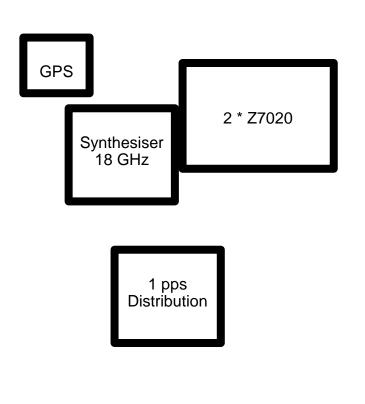

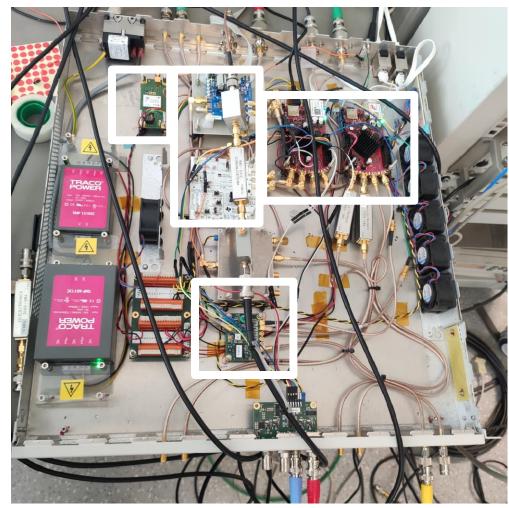

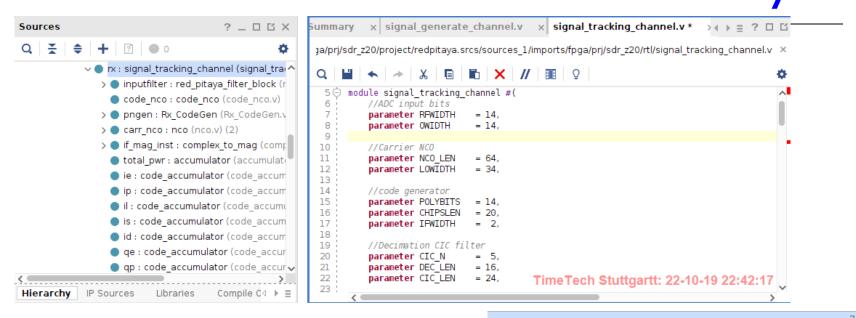

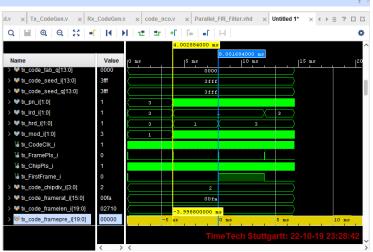

#### Breadboarding: Digital SATRE: Tx and Rx, direct sampling receiver

#### **Breadoarding: Development Chain**

Development Chain, incl.

- All-VHDL implementation

- No copyrighted libraries

- Bitwise Simulation

#### **Beardboarding: Development and Verification**

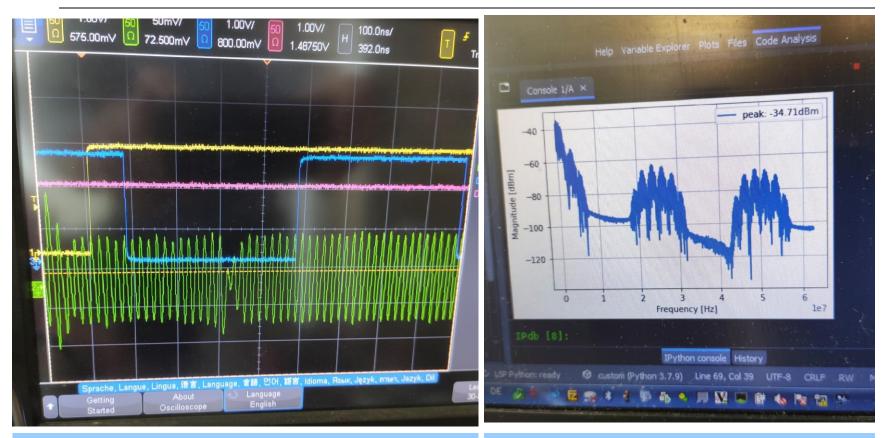

#### Digital Signal Analysis Internal Test Points, DAC output to Scope

- 1 pps

- PN Sequency

- Modulated RF

Numerical Signal analysis, incl FFT

#### Zero IF, showing data modulation

• Major elements realised in FPGA

> 40x FPGA cores developed / verified by test bench incl.

different DDS appoarches, look-up table & CORDIC, PID controller, modulation, demodulation, saturation, complex multiplier, decimator etc.

- Major C code elements incl. FPGA DDR interface, data streaming, FFT etc, running on embedded ARM cores in ZYNQ SoC

- Code re-use from SATRE, but complied in high level

language

- Low-cost MWL G/T is not commercially feasible, reproduction of G/T impossible due to obsolescense

- Chip-shortage prohibits any fast solution

- "Market research": Investment too high for a short mission like ACES

- ACES MWL: Lets optimise, what is available

- Maximise operational outputs

- Aim for highest possible chip rates

- Direct Sampling is complex for BW above few 100 MHz, although this is definitely the future

- Allows for multi-channel operation

- But: Not ready "now"

- MWL-Rx mixed signal architecture can be scaled to 1 GSa/s and above, ground and space, But single channel reception only

- In the near term, ACES-MWL architecture is most promising

- Traditional bent-pipe transponders have limited capabilities, even at very high BW (500 MHz and up)

- Better use on-board signal regeneration, multiple channel operation, all links like ACES-MWL

- Downlink the translation oscillator as separate signal

- Transmit coherent carrier and modulation, cycle identification

- 32, 48 GHz and up

### Plan for dedicated, optimised transponder(s) in GEO orbit, optimise footprint